Chương 4. Bộ đếm _ Phần 1

Lập trình nhúng với STM32-Chương 4. Lập trình thời gian thực (Phần 1) |Realtime Programing for STM32Подробнее

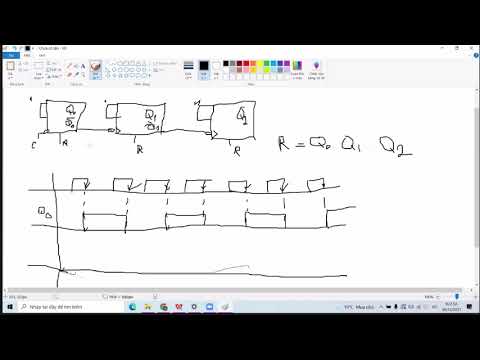

kts chương 4 mạch đếm KĐB - 1Подробнее

Verilog. Bài 441: Mạch đếm Johnson 16 bit PST. Chương 4: Thiết kế mạch tuần tự 1.Подробнее

KTS CHƯƠNG 4 P2 MẠCH ĐẾMПодробнее

KTS CHƯƠNG 4 P1 FLIP FLOPПодробнее

KTS CHƯƠNG 4 P3 DẠNG SÓNG NGÕ RAПодробнее

Verilog. Bài 424: Đếm nhị phân 8 bit: có ena5hz, ena_ss, ena_ud. Chương 4: Thiết kế mạch tuần tự 1.Подробнее

VHDL – FPGA. Bài 435: Đếm nhị phân 1 bit bằng 1 nút nhấn. Chương 4: TKM tuần tự 1.Подробнее

VHDL – FPGA. Bài 438: Đếm nhị phân 4 bit Up/Dw bằng 2 nút nhấn. Chương 4: Thiết kế mạch tuần tự 1.Подробнее

VHDL – FPGA. Bài 430: đếm ngẫu nhiên 3 bit. Chương 4: Thiết kế mạch tuần tự 1.Подробнее

VHDL – FPGA. Bài 425: Đếm nhị phân 8 bit theo ena5hz, có ena_ss ena_ud tự động. Chương 4: TKM TT1.Подробнее

VHDL – FPGA. Bài 424: Đếm nhị phân 8 bit theo ena5hz, có ena_ss, ena_ud. Chương 4: TKM tuần tự 1.Подробнее

VHDL – FPGA. Bài 423: Đếm nhị phân 8 bit theo ena5hz, có ena_ss. Chương 4: Thiết kế mạch tuần tự 1.Подробнее

VHDL – FPGA. Bài 421: Đếm nhị phân 4 bit theo tín hiệu ENA1Hz. Chương 4: Thiết kế mạch tuần tự 1.Подробнее

VHDL – FPGA. Phần 1. Giới thiệu. Chương 4: Thiết kế mạch tuần tự 1.Подробнее

Logisim | Bộ Đếm Lên Xuống 4,8,16 và 32 Bit Dùng D Flip Flop | Binary Up Down CounterПодробнее

Chương 4. Bộ đếm - Phần 3Подробнее

Chương 4. Bộ đếm_Phần 2Подробнее

kỹ thuật điện tử số. Tuần 14 . Chương 4. Bộ đếm.Подробнее